### US005206524A

#### United States Patent [19] Patent Number: [11]

5,206,524

Date of Patent: [45]

Apr. 27, 1993

# [54] HETEROSTRUCTURE BIPOLAR TRANSISTOR

[75] Inventors: Young-Kai Chen, Berkeley Heights;

Anthony F. J. Levi, Summit, both of N.J.; Richard N. Nottenburg, New York, N.Y.; Morton Panish,

Springfield, N.J.

AT&T Bell Laboratories, Murray [73] Assignee:

Hill, N.J.

[21] Appl. No.: 721,913

Chen et al.

Jun. 20, 1991 [22] Filed:

# Related U.S. Application Data

Continuation of Ser. No. 511,872, Apr. 19, 1990, abandoned, which is a continuation of Ser. No. 250,790, Sep. 28, 1988, abandoned.

| [51] | Int. Cl.5 | <br>    | HU   | 1L 29 | 772  |

|------|-----------|---------|------|-------|------|

| [52] | U.S. Cl.  | <br>257 | /29; | 257/  | 198; |

| £3   |           |         | -    | 257/  |      |

[58] Field of Search ............. 357/34 HB, 16, 61, 30 E

#### [56] References Cited

#### U.S. PATENT DOCUMENTS

| 4,617,724 | 10/1986 | Yokoyama et al 357/34  |

|-----------|---------|------------------------|

| 4,672,404 | 6/1987  | Ankri et al 357/34     |

| 4,710,936 | 12/1987 | Shibata et al 357/16   |

| 4,758,870 | 7/1988  | Hase et al 357/34      |

| 4,768,074 | 8/1988  | Yoshida et al 357/34   |

| 4,825,265 | 4/1989  | Lunardi et al 357/34   |

| 4.827.320 | 5/1989  | Morkoc et al 357/55    |

| 4.829,343 | 5/1989  | Levi 357/61            |

| 4.829.347 | 5/1989  | Cheng et al 357/16     |

| 4,833,511 | 5/1989  | Sugimoto 357/30 E      |

| 4.926.232 | 5/1990  | Ando et al 357/34      |

| 5,031,005 | 7/1991  | Futatsugi et al 357/16 |

|           |         |                        |

# FOREIGN PATENT DOCUMENTS

|           |         | European Pat. Off |

|-----------|---------|-------------------|

| 60-010774 | 1/1985  | Japan 357/16      |

| 60-010775 | 1/1985  | Japan 357/16      |

| 61-04279  | 1/1986  | Japan 357/34 HB   |

| 61-226961 | 10/1986 | Japan 357/34 HB   |

| 62-229878 | 10/1987 | Japan 357/34 HB   |

| 63-006878 | 1/1988  | Japan 357/16      |

#### 63-156356 6/1988 Japan ...... 357/34 HB 2128026 4/1984 United Kingdom .......... 357/34 HB

# OTHER PUBLICATIONS

Das. M. "High-Frequency Performance Limitations . . . " IEEE Trans. Elec. Dev. May 1988, pp. 604-614. Kroemer, "HBTs & ICs," Proc. of the IEEE, vol. 70, No. 1, pp. 13-25, Jan. 1982.

(List continued on next page.)

Primary Examiner-Andrew J. James Assistant Examiner-Sara W. Crane Attorney, Agent, or Firm-E. E. Pacher

#### ABSTRACT [57]

Improved heterojunction bipolar transistor (HBT) are disclosed. Inventive devices can attain high cut-off frequency (f<sub>T</sub>), exemplarily 80 GHz or higher, and high DC current gain  $(\beta)$ , exemplarily 25 or higher. The devices exhibit lateral scaling, permitting reduction in emitter stripe width without unacceptable decrease in B. Exemplarily the stripe width is 1 µm or less. The inventive HBTs are hot electron devices, with the hot electrons in the base region being spatially confined such that relatively few electrons reach the surface of the extrinsic base region. The relatively low bulk and surface recombination rate in the base of inventive HBTs is an important aspect of the invention and makes possible devices having relatively high  $\beta$  and low power consumption. Appropriate choice of base material, namely, a semiconductor material having relatively low intrinsic surface recombination velocity, can result in further reduction of surface recombination, as can, for instance, the use of an appropriate non-alloyed metal base contact. Appropriate choice of collector material can result in improved ballistic transport through the collector depletion region, and novel selection criteria are disclosed. InP, InAs, and In0.53Ga0.47As are exemplary materials that meet these criteria. Use of a highly doped collector contact region, with dopant level within a relatively narrow concentration range, can also lead to improved device behavior, as can the use of a compound emitter that comprises one or more appropriately placed thin undoped heteroepitaxial layers.

8 Claims, 5 Drawing Sheets

## OTHER PUBLICATIONS

Sugiura et al., "High-Current-Gain In GaAs/InP Double HBT Grown by Metal Organic Vapor Phase Epitaxy," IEEE Elec. Dev. Let., vol. 9, No. 5, pp. 253-255, May 1988.

Ishibashi et al., "A Novel AlGaAs/GaAs HBT Structure for Near Ballistic Collection," IEEE Trans. on. Elec. Dev., vol: ED-34, pp. 237, Nov. 1987.

Malik et al., "High Gain Al<sub>0.48</sub>In<sub>0.52</sub>As/Ga<sub>0.53</sub>As Vertical n-p-n HBTs Grown by MBE," IEEE Elec. Dev. Let., vol. EDL-4, No. 10, pp. 383-385, Oct. 1983.

Fukano et al., "High-Speed InA/As HBTs," IEEE Elec. Dev. Let., vol. 9, No. 6, pp. 312-315, Jun. 1988. Nagata et al., "Self-Aligned AlGaAs/GaAs HBT w/Low Emitter Resistance...", IEEE Trans. on Elec. Dev., vol. ED-35, No. 1, pp. 2-7 Jan. 1988.

Asbeck et al., "Numerical Simulation of GaAs/GaAlAs ...", IEEE Elec. Dev. Let., vol. EDL-3, No. 12, pp. 403-406, Dec. 1982.

Asbeck et al., "HBTs for Microwave & Millimeter-Wave I.C.," IEEE Trans. on Elec. Dev., vol. ED-34, No. 12, pp. 2571-2579, Dec. 1987.

Chang et al., "AlGaAs/GaAs HBTs Fabricated Using a Self-Align Dual-Lift-Off Process," IEEE Elec. Dev. Let., vol. EDL-8, No. 7, pp. 303-305, Jul. 1987.

Tully, "HBTs with Ion Implanted Bases," IEEE Elec. Dev. Let, vol. EDL-7, No. 4, pp. 203-205, Apr. 1986. Asbeck et al., "GaAs/GaAlAs HBTs w/Cutoff Freq. Above 10 GHz," IEEE Elec. Dev. Let., vol. EDL-3, No. 12. Dec. 1982.

Ishibashi, "A Possible Near-Ballistic Collection in an AlGaAs/GaAs HBT w/A Modified Collector Structure," IEEE Tras. Elec. Dev., vol. 35, No. 4, pp. 401-404, Apr. 1988.

Nagata et al., "High-Speed Performance of AlGaAs/-GaAs HBTs w/Nonalloy Emitter Contacts", IEEE Trans. Elec. Dev., vol. ED-34, p. 2369, Nov. 1987. Chen, Reddy, Moi, Peng, Morkoc; Enhanced Ballistic Transport. in InGaAs/InAlAs hot-electron transistor, Jul. 23, 1987, pp. 1254-1255.

Hayes et al, Hot electron transport in a graded band-gap base heterojunction bipolar transistor, Apr. 18, 1988, pp. 490-492 Appl. Phys. Lett.

Ramberg et al, Lattice-strained heterojunction In-GaAs/GaAs bipolar structures:Recombination properties and Device performance, pp. 1234–1236 J. Appl. Phys.

Kuzuhara, Transient Simul. of AlGaAs/GaAs/AlGaAs and AlGaAs/InGaAs/AlGaAs HETs., Jan. 1, 1989, IEEE Transactions on Electron Devices.

"Scaling 'Ballistic' Heterojunction Bipolar Transistors", by A. F. J. Levi, Electronics Letters, vol. 24, No. 20, Sep. 29, 1988, pp. 1273-1275.

"Submicron Scaling of AlGaAs/GaAs Self-Aligned Thin Emitter Heterojunction Bipolar Transistors (SA-TE-HBT) With Current Gain Independent of Emitter Area", by R. J. Malik, *Electronics Letters*, Aug. 17, 1989, vol. 25, No. 17, pp. 1175-1177.

"High Gain InGaAs/InP Heterostructure Bipolar Transistors Grown by Gas Source Molecular Beam Epitaxy", by R. N. Nottenburg, Applied Physics Letters, 49(17), Oct. 27, 1986, pp. 1112-1114.

"InGaAs/InAlGaAs Hot-Electron Transistors With Current Gain of 15", by K. Imamura et al., *Electronics Letters*, vol. 22, No. 21, Oct. 1986, pp. 1143-1150. *IEEE Spectrum*, Feb. 1986, "The Quest for Ballistic Action" by T. E. Bell, pp. 36-38.

IEEE Spectrum, Feb. 1986, "Ballistic Electrons in Compound Semiconductor" by L. F. Eastman, pp. 42-45. IEEE Electron Device Letters, vol. EDL-8, No. 5, May 1987, "Submicrometer Fully Self-Aligned AlGaAs/GaAs Heterojunction Bipolar Transistor" by N. Hayama et al, pp. 246-248.

IEEE Transactions on Electronic Devices, vol. ED-33, No. 4, Apr. 1986, "A 30-ps Si Bipolar Ic Using Super Self-Aligned Process Technology", by S. Konaka et al, pp. 526-531.

FIG. 1

FIG. 2

U.S. Patent

FIG. 5 I<sub>c</sub>(2mA/DIVISION) V<sub>ce</sub>(500mV/DIVISION)

**FIG.** 7

FIG. 8

# HETEROSTRUCTURE BIPOLAR TRANSISTOR

This application is a continuation of application Ser. No.07/511,872, filed on Apr. 19, 1990, now abandoned 5 which is a continuation of application Ser. No. 07/250,790, filed on Sep. 28, 1988, now abandoned.

### FIELD OF THE INVENTION

This application pertains to the field of active semi- 10 conductor devices. In particular, it pertains to heterostructure bipolar transistors in which at least some of the current is carried by hot electrons.

## BACKGROUND OF THE INVENTION

It has been known for some time that a hot electron transistor could potentially be operated at frequencies in excess of those achievable with conventional (diffusive) transistors. See, for instance, T. E. Bell, IEEE Spectrum, February 1986, pp. 36-38, incorporated herein by refer- 20 ence. Various types of hot electron transistors (HET) have been proposed. This application is concerned with one particular class of such transistors, namely, hot electron heterojunction bipolar transistors (HBTs). For a brief review, see L. F. Eastman, ibid, pp. 42-45, also 25 incorporated herein by reference.

The flow of electrons from emitter to collector in a bipolar transistor is controlled by varying the emitter/base barrier potential by means of an applied voltage Veb, and is also a function of an externally applied volt- 30 age V<sub>bc</sub> between base and collector. Under normal operating conditions, V<sub>bc</sub> reverse biases the base/collector junction. Electrons injected from the emitter into the base of a bipolar HET have energy substantially greater base. These "hot" electrons ideally should traverse the base and collector depletion region without undergoing significant scattering, and enter the sea of conduction electrons in the collector contact region.

As will be readily understood by those skilled in the 40 art, substantial difficulties have to be overcome before a device of this type can function as a practical HET. Among these is the difficulty of achieving substantial hot electron transport through the base and the depletion region of the collector.

Three recently filed U.S. patent applications Ser. No. 871,494, filed Jun. 6, 1986 by J. R. Hayes et al; Ser. No. 074,127, filed Jul. 17, 1987, by A. F. J. Levi; and Ser. No. 241,279, filed Sep. 7, 1988 by A. F. J. Levi, all incorporated herein by reference), disclose means for 50 achieving improved HETs. However, in view of the general desirability of improved characteristics such as larger DC current gain  $\beta$  (defined as collector current  $I_c$  divided by base current  $I_b$ ) and high cut-off frequency f<sub>T</sub>, means for achieving further improvements in HET 55 characteristics would be of considerable significance.

In prior art HBTs the emitter stripe width is relatively large, typically at least about 1 µm and, to the best of our knowledge, has not been less than 0.6 µm even in a laboratory device that had quite low  $\beta$  (from 60 the data reported it can be deduced to have been about 16; see N. Hayama et al, IEEE Electron Device Letters, Vol. EDL-8(5), May 1987, pp. 246-248). To the best of our knowledge, the prior art has not succeeded in making a HBT which combines at room temperature a large 65  $f_T(\ge 80 \text{ GHz})$  with a large  $(\ge 25) \beta$  and small  $(\ge 1 \mu\text{m})$ emitter stripe width. This is to be contrasted with Si bipolar transistors in which high performance and stripe

widths as small as 0.35 µm have been achieved (see S. Honaka et al, IEEE Transactions on Electronic Devices, Vol. ED-33, pp. 526-531, 1986). As is well known to those skilled in the art, narrow emitter stripe width is advantageous since it can, inter alia, result in lower power consumption at a constant current density (and thus make possible larger scale integration), or in increased speed at a constant current (and thus constant

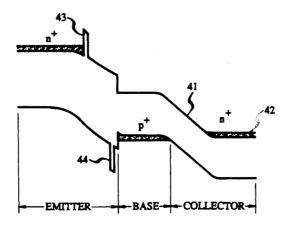

In a prior art (diffusive) bipolar transistor electrons are injected from the emitter stripe into the base, with the base typically being substantially wider than the emitter stripe (a bipolar transistor structure is schematically depicted in FIG. 1). The base region that underlies 15 the emitter stripe is frequently referred to as the "intrinsic" base region, and the base regions that do not underlie the emitter stripe as the "extrinsic" base regions. It is to be noted that in this context "intrinsic" has nothing to do with the dopant concentration in the base region.

Electrons injected into the intrinsic base region of a (diffusive) bipolar transistor undergo diffusive motion, and some of these minority carriers undergo recombination, a process which, inter alia, results in decreased  $\beta$ . Recombination can take place both in the bulk base region and on the exposed surfaces of the (extrinsic) base region. Associated with any semiconductor material is an intrinsic surface recombination velocity So. For instance, in silicon  $S_0$  is approximately 10 cm/sec, whereas in GaAs it is about 106 cm/sec.

As will be readily appreciated by those skilled in the art, surface recombination in general becomes of increasing importance as the emitter stripe width is decreased. Due to the relatively small So of Si it is possible to make transistors that have small stripe width and yet than the thermal energy of the ambient electrons in the 35 have acceptable values of  $\beta$ . However, due at least in part to the much larger So of GaAs it has not been possible to similarly reduce the stripe width of GaAs HBTs without causing unacceptable degradation of  $\beta$ . As is well known, most of the work on HBTs has so far been done on GaAs-based devices. From the above discussion it can be seen that the relatively large stripe width of prior art HBTs generally is a deliberate design choice and is not due to any processing limitation.

#### **DEFINITIONS**

Electron transport in a crystal is herein defined to be "ballistic" if, in addition to its possible interaction with an accelerating electric field, the electron interacts substantially only with the static part of the periodic lattice potential. Electron transport thus may be ballistic even through the electrons undergo some small angle scattering and/or small energy change.

A conduction electron herein is considered to be a "hot" electron in a given semiconductor region if its energy E is substantially greater than the ambient thermal energy  $k_BT$ . Typically,  $E \gtrsim 8k_BT$ , where  $k_B$  is the Boltzmann constant, and T is the absolute temperature of the lattice.

A "hot electron" transistor (HET) is a transistor whose operative characteristics are in substantial part determined by the transport of hot electrons through the transit region of the transistor, with minimal scattering of the hot electrons in the transit region.

The "transit region" of a HET herein is that portion of the HET through which substantial hot electron transport takes place, or is intended to take place. For instance, in a bipolar transistor, the transit region consists of the base and the collector depletion region. In 3,200,3

order to have the possibility of significant hot electron transport in a HET, the width of the transit region has to be less than the mean-free path of the hot electrons in the material.

The "ambient" charge carriers are those charge carriers (electrons or holes) that are essentially in thermal

equilibrium with the lattice. For instance, in n-p-n

HBTs the ambient charge carriers in the base are holes.

#### SUMMARY OF THE INVENTION

Broadly speaking this application discloses HBTs having improved device characteristics, exemplarily high current gain, high cut-off frequency, and/or low power dissipation. Transistors according to the invention typically will have device geometries that are similar to those of prior art HBTs (preferably including the relatively thin transit region disclosed in the above referred to '279 U.S. patent application), but will typically have substantially reduced emitter stripe width and/or comprise collector material that meets certain 20 novel criteria. Other optional design features, to be discussed below, may also be present.

HBTs according to the invention comprise, in addition to the emitter region, a collector region and a base region intermediate and in contact with the emitter and 25 collector regions, and further comprise means for making electrical contact with the emitter region, the base region, and the collector region. The inventive transistors are hot electron transistors, that is, they are of a type wherein, under normal operating conditions, hot 30 electrons are caused to be injected from the emitter into the base region. In at least some preferred embodiments the collector comprises a semiconductor material wherein E<sub>bw</sub>-E<sub>g</sub> is greater than about 0.6 eV, where  $E_{bw}$  and  $E_{g}$  are the conduction band width and bandgap 35 energy of the semiconductor material. In some preferred embodiments the semiconductor material is furthermore selected to have  $\Delta_{\Gamma-x}=E_{\Gamma-x}-E_g\geq 0$ , where  $E_{\Gamma-x}$  is the separation in energy between the  $\Gamma$ minimum and the X-minimum in the conduction band of 40 the material. Exemplarily, In<sub>0.53</sub>Ga<sub>0.47</sub>As, InAs and InP have  $\Delta_{\Gamma-x}$  of about 0.4 eV, 1.45 eV, and 0.45, respectively.

In at least some preferred devices the collector material also meets the criterion that  $\Delta_{\Gamma-L}=E_{\Gamma-}$ . 45  $_L-E_g \ge -0.2$  eV, where  $E_{\Gamma-L}$  is the separation in energy between the  $\Gamma$ -minimum and the L-minimum in the conduction band. Exemplarily,  $I_{10.53}Ga_{0.47}As$ ,  $I_{10.53}Ga_{0$

Use of semiconductor material that meets the first (preferably both) of the above criteria can result in a HBT in which a substantial fraction of the electron transport in the collector depletion region is ballistic. It can also result in a device whose cut-off frequency is 55 substantially independent of  $V_{bc}$  over a voltage range that is compatible with current semiconductor technology. Exemplarily, for  $In_{0.53}Ga_{0.47}As$  this range of  $V_{bc}$  is between about 0 and about 0.4 volts, a convenient range for switching and other technologically significant applications.

In at least some preferred embodiments of the invention under normal operating conditions at least a significant fraction of the hot electrons injected into the base can traverse the base region without undergoing substantial scattering therein, the device has operating characteristics unattained by prior art HBTs (typically  $f_T \ge 80$  GHz and  $\beta \gtrsim 25$ , both at room temperature), and

the emitter stripe has a width that is equal to or less than about 1  $\mu$ m. Differently stated, inventive HBTs can have an emitter stripe width W that is less than that of a diffusive HBT having the same  $\beta$  and  $f_T$ . If  $f_T$  of the inventive HBT is too large to be matched by any diffusive HBT then the diffusive comparison HBT is to have a  $f_T$  of at least 80 GHz.

The hot electrons injected into the base of an inventive transistor do not diffuse in the base but traverse the base more or less ballistically, spatially confined, in the form of a more or less well defined (diverging) beam of hot electrons. This mode of electron transport results in reduced likelihood of surface recombination, as manifested by substantial lateral scaling of inventive transistors. This makes possible a substantial reduction of the emitter stripe width without incurring the substantial decrease of β associated with prior art GaAs HBTs. In particularly preferred embodiments, the base region comprises a semiconductor material whose surface recombination velocity is substantially less than about 105 cm/sec, whereby surface recombination is still further reduced. Exemplarily, In<sub>0.53</sub>Ga<sub>0.47</sub>As is such a material.

HBTs with narrow emitter stripe according to the invention can have relatively low power dissipation for a given operating current density and thus are more suitable for large scale integration than prior art GaAsbased HBTs. Furthermore, due to low surface recombination, transistors according to the invention can have higher  $f_T$  than is obtainable in comparable prior art devices. Inventive transistors can find application in, for example, high speed, low power, digital and analog integrated circuits for high speed computers and fiber optic communication systems. Due to the improved lateral device scaling inventive HBTs can also advantageously be used in relatively high (>10 GHz) and moderate (<10 GHz) speed applications where small emitter stripe widths are required. Significantly, at least in some embodiments the inventive HBTs are well adapted to integration with optical and/or opto-electronic devices, especially such devices that are designed to operate at relatively long wavelengths, e.g., in the range 1.3—1.6 μm. This wavelength regime is currently preferred for fiber optical communications. Thus we contemplate apparatus and systems comprising one or more HBTs according to the invention and one or more optical or optoelectronic devices whose operating wavelength lies in the infrared part of the electromagnetic spectrum functionally integrated on or in a common semiconductor substrate, exemplarily an InP wafer 50 or chip.

## **BRIEF DESCRIPTION OF THE DRAWINGS**

FIG. 1 schematically depicts a device according to the invention;

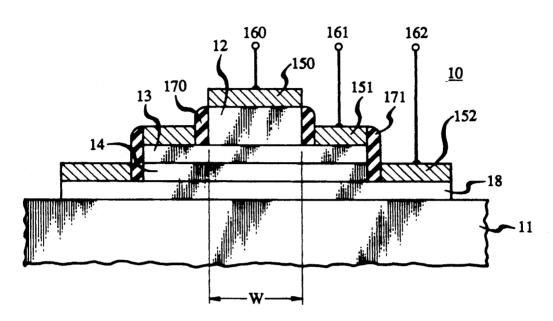

FIG. 2 schematically illustrates some features of the band structure of a semiconductor material;

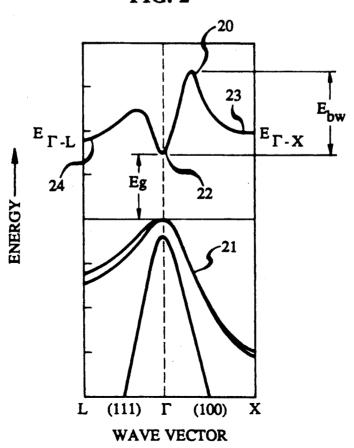

FIG. 3 shows exemplary curves of small signal current gain vs. collector current for transistors having different emitter stripe width;

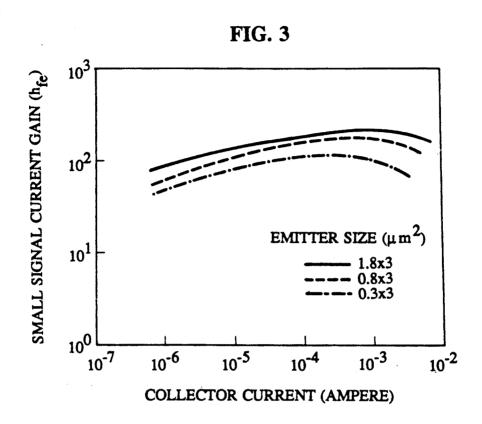

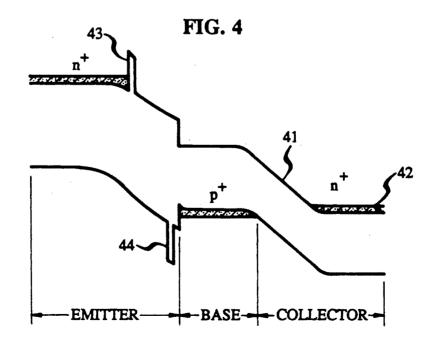

FIG. 4 schematically shows the relevant valance and conduction band edges in an exemplary device according to the invention;

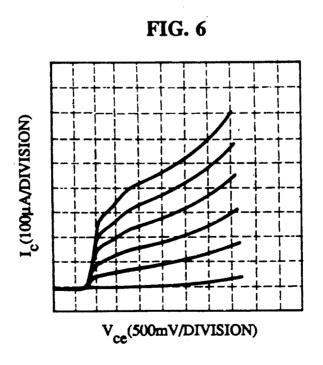

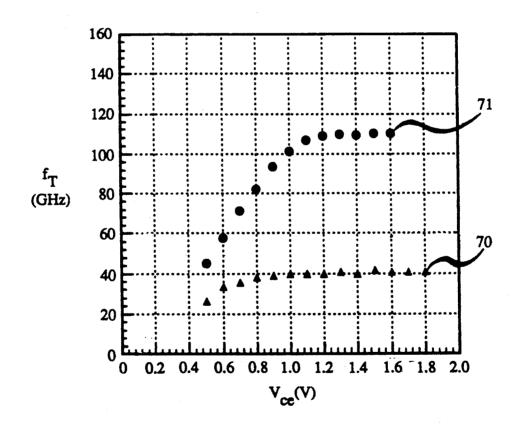

FIGS. 5 and 6 show the common emitter characteristics for two exemplary HBTs that differ in emitter size; FIG. 7 shows f<sub>T</sub>vs. V<sub>ce</sub> of an exemplary HBT according to the invention; and

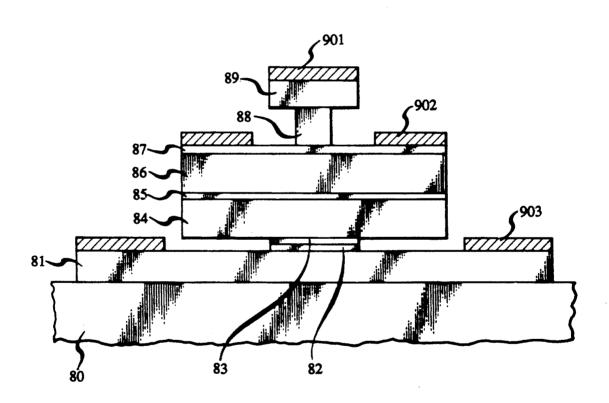

FIG. 8 schematically depicts an exemplary inventive HBT.

5

The figures are not necessarily drawn to scale, nor are the relative proportions intended to be accurate.

#### DETAILED DESCRIPTION OF SOME PREFERRED EMBODIMENTS

FIG. 1 schematically depicts an exemplary HBT according to the invention. The transistor 10 comprises substrate 11, with collector contact region 18, collector depletion region 14, base region 13, and emitter region 12 being epitaxial with the respective adjacent regions 10 and/or substrate. Typically the substrate is semi-insulating semiconductor material, collector and base region can (but need not) comprise the same semiconductor material as the substrate, and the emitter comprises semiconductor material that differs from that of the 15 base. FIG. 1 also shows contact means 150, 151, and 152, and insulators 170 and 171 placed to prevent shorting. Indicated are also means 160, 161, and 162 for making electrical contact with the emitter, base, and collector regions, respectively. In many embodiments inventive HBTs have an elongate emitter region (the emitter "stripe") of width W. As will be appreciated by those skilled in the art, FIG. 1 is exemplary only and, for instance, HBTs having an inverted structure are also possible.

Those skilled in the art are familiar with techniques and processes that can be used to produce HBTs of the type relevant to this application. These processes comprise epitaxial growth processes such as molecular beam epitaxy or metal-organic chemical vapor deposition, ion implantation, rapid thermal annealing, lithography, and wet or dry etching.

FIG. 2 shows relevant portions of the energy band structure of an exemplary semiconductor. Such diagrams are well understood by those skilled in the art and do not require detailed explanation. In particular, FIG. 2 shows the conduction band edge 20 and the valence band edge 21, with the former comprising the Γ-minimum 22, the X-minimum 23 and the L-minimum 24. The figure also shows the significance of the bandgap energy  $E_g$  and of the energy differences  $E_{\Gamma-X}$  and  $E_{\Gamma-L}$ . Many of the semiconductors of interest herein have an energy band structure qualitatively similar to that shown in FIG. 2. The band structures of semiconductors of current technological interest are well known; however, if the band structure for a semiconductor is not currently known then it can be readily calculated by known techniques, e.g., the pseudopoten-

The art has long sought to find ways of minimizing the scattering of the hot electrons in the transit region of a HET. In the above referred to '279 U.S. patent application, it was, inter alia, disclosed that such scattering can be decreased if the transit region comprises (typically, the base region and collector region consist of) semiconductor material having

$E_{bw}-E_g \gtrsim 0.6 eV$ .

Furthermore, FIG. 3 of the '279 application shows that in p-GaAs the inelastic scattering rate of hot electrons 60 decreases with increasing dopant concentration above a dopant concentration that is a function of the average energy  $E_i$  of the hot electrons. For instance, it is shown there that for  $E_i=200$  meV the inelastic scattering rate about  $2 \times 10^{19}$  cm<sup>-3</sup>. It is also disclosed in the '279 application that similar results apply to other compound semiconductor materials useful for hot electron bipolar

6

transistors. As is shown in more detail below, an acceptable value for  $E_i$  in an exemplary hot electron transistor according to the invention is about 200 meV. Thus, exemplary incentive transistors typically will have base doping levels of at least about  $2 \times 10^{19}$  cm<sup>-3</sup>.

We have discovered further requirements which can lead to further reduction of scattering of the hot electrons in the collector depletion region of HBTs according to the invention. One of these requirements is  $\Delta_{\Gamma-X}=E_{\Gamma-X}-E_{g}\geq 0$ . In devices that do not meet this condition output impedance will typically be low and the number of ballistic electrons that can transit the collector depletion region will also be relatively low. Exemplary semiconductors that meet this requirement are  $In_{0.53}Ga_{0.47}As$  ( $\Delta_{\Gamma-\chi}=0.4$  eV), InAs (1.45 eV), and InP (0.45 eV). Use of a semiconductor material that meets the above requirement to form the collector region can lead to a substantial improvement in the ballistic transport in the collector depletion region (which in turn can result in improved  $\beta$ ) for reasonable values of  $V_{bc}$ , and at least some currently preferred transistors according to the invention comprise a collector region and base region made from semiconductor material that meets the above requirement.

The above requirement insures that in the collector depletion region the rate of scattering from the  $\Gamma$ -valley into the X-valley can be small for reasonable values of  $V_{bc}$ . Since  $\Gamma \rightarrow X$  scattering is potentially a very impor-30 tant scattering mechanism its absence or decreased likelihood can lead to substantial improvement in the current gain. A further scattering mechanism which typically is also of some (although typically lesser) importance is  $\Gamma \rightarrow L$  scattering. By choosing a collector material having  $\Delta_{\Gamma-L} = E_{\Gamma-L} - E_g \ge -0.2 \text{ eV } \Gamma \rightarrow L \text{ scatter-}$ ing can be substantially reduced. Failure to meet this criterion has similar (but typically less severe) consequences than failure to meet the  $\Delta\Gamma$ -X criterion. Exemplary semiconductor materials that meet this criterion are  $In_{0.53}Ga_{0.47}As$  ( $\Delta_{\Gamma-L} = -0.2$  eV), InAs (0.55 eV), and InP (-0.2 eV).

The above criteria (preferably together with the previously disclosed criterion  $E_{bw}-E_{g}\gtrsim 0.6$  eV) defines a class of semiconductor materials which can be advantageously used as collector material in hot electron HBTs since the choice can result in devices in which a substantial fraction of the electron transport in the collector depletion region is ballistic. This choice of collector material can furthermore result in a transistor whose cut-off frequency is substantially independent of V<sub>bc</sub> over a significant (and technologically useful) voltage range, a characteristic typically not found in prior art HBTs. Exemplarily, for In<sub>0.53</sub>Ga<sub>0.47</sub>As this range of  $V_{bc}$  is from about 0 to about 0.4 V.

We have also discovered that it is possible to substantially reduce the emitter size of an appropriately designed HBT without incurring an unacceptably large decrease in  $\beta$ . At least some preferred HBTs according to the invention thus have an emitter size that is comparable to emitter size in analogous state of the art Si devices and that is substantially smaller than that currently used in high speed GaAs-based HBTs. In particular, these preferred devices typically have an emitter stripe width W (see FIG. 1) of less than about 1 µm, decreases with increasing dopant concentration above 65 preferably no more than about 0.5 µm, while having β≳25.

The above referred to reduction in W without attendant unacceptable decrease in  $\beta$  is possible if the elec-

trons injected into the base from the emitter are hot electrons (typically  $E_i \gtrsim 0.2$  eV, where  $E_i$  is the average energy of the injected hot electrons), and such that at least a substantial portion of the injected hot electrons are spatially confined in the base. A necessary condition 5 for this to occur is that there is a substantial likelihood that an electron can traverse the base region without undergoing substantial scattering therein. Some techniques that can result in low scattering in the bulk of the base region are disclosed in the '279 U.S. patent applica- 10 tion.

Hot electrons injected into the base region over an abrupt heterojunction have a high velocity (exemplarily about 108 cm/sec) compared to that of the electrons in "diffusive" transistors (about 107 cm/sec). Further- 15 more, the hot electrons are injected into the base in beam-like manner, with the average angle of divergence of the "beam"  $\langle \theta \rangle$  being about  $\tan^{-1} (k_B T/E_i)^{0.5}$ . Typically in inventive HBTs  $<\theta>$  is less than about 20°.

Due to the high velocity, beam-like injection with relatively low  $\langle \theta \rangle$  and substantially ballistic transport through the base the rate of non-radiative recombination in the bulk of the base and on the extrinsic base region surfaces of at least some inventive HBTs can be 25 substantially lower than in diffusive devices, making possible significantly larger  $\beta$  in such ballistic HBTs, as compared to diffusive HBTs. In ballistic HBTs an increase in  $\beta$  can also result from a reduction in  $Z_b$ , the thickness of the base layer, and  $Z_b \lesssim 100 \text{ nm}$  is preferred. 30

Furthermore, appropriate choice of base material can result in a substantial further reduction of surface recombination. Advantageously the base material has So that is less than about 105 cm/sec, preferably as much as a factor of 10 less or even smaller. For instance, In<sub>0.5</sub>. 35 3Ga<sub>0.47</sub>As has S<sub>0</sub> of about 10<sup>3</sup> cm/sec. InP and InAs also meet the above inequality. In many cases it will be advantageous to use a non-alloyed metal contact, a degenerate semiconductor contact, or a combination of these, as a base contact, since this may result in a further 40 increase in the minority carrier lifetime in the extrinsic base region if the contacts are formed such that the surface recombination on the extrinsic base region surface is not substantially increased above  $S_0$  of the base material. Evaporation of the metal layer is believed to 45 be a deposition method that will not substantially increase surface recombination, whereas sputtering is likely to result in an increase.

In FIG. 3 are shown exemplary results of (small signal) current gain vs. collector current, for three HBTs 50 that were identical except for the width W of the emitter stripe. The transistors had an InP emitter (n-type,  $5 \times 10^{17}$  cm<sup>-3</sup>), a 65 nm thick p<sup>+</sup>( $5 \times 10^{19}$ ) base, a 300 nm thick  $n-(1.5\times10^{16})$  collector depletion region and a 500 nm thick  $n+(5\times10^{19})$  collector contact region, with 55 the last three regions being In<sub>0.53</sub>Ga<sub>0.47</sub>As. All three devices have a collector area of  $9.6 \times 10^{-7}$  cm<sup>2</sup>. As can be seen from the figure, the decrease in W results in a relatively minor decrease in the current gain, and the maximum (room temperature) small signal current gain 60 Exemplarily, for a In<sub>0.53</sub>Ga<sub>0.47</sub>As transit region of the of the transistor with smallest W is significantly greater than 100. Inventive devices will generally have room temperature  $\beta \ge 25$ .

As will be appreciated by those skilled in the art, reduction in W without attendant significant decrease in 65  $\beta$  can make possible increased large scale integration, not only because device size can be shrunk but, significantly, because power dissipation can be substantially

lower, resulting in greatly reduced thermal load. Reduced emitter size of course can also result in smaller capacitance and thus potentially in higher cut-off frequency. Reduced recombination in the base also results in reduced power consumption.

We have discovered still other (optional) means that can result in improved performance in hot electron HBTs. A HBT typically operates by transforming a low impedance current source (the emitter current) into a high impedance current source (the collector current). In diffusive HBTs the scattering that takes place in the collector depletion region is a significant aspect of this impedance transformation. In inventive hot electron HBTs the current flow in the collector depletion region is substantially ballistic, and thus no impedance transformation takes place in the collector depletion region. Instead the transformation has to occur in the collector contact layer. This is achieved if the ballistic electrons that enter the contact region suffer (irreversible) scattering that thermalizes the electrons.

Most efficient scattering (and hence rapid impedance transformation) occurs if the plasma frequency of the contact region layer  $(f_p)$  satisfies  $hf_p \ge E_c$ , where h is Planck's constant and  $E_c$  is the average energy of the electrons arriving at the collector contact. Under normal operating conditions in a ballistic HBT E<sub>c</sub>~E<sub>g</sub>. Thus the condition can also be written as  $hf_p \lesssim E_g$ . As is well known, the plasma frequency is related to the carrier concentration n by  $f_n = (ne^2/\pi \epsilon m^* m_o)^{\frac{1}{2}}$ , where e is the electron charge,  $\epsilon$  is the permittivity of the medium, and m\* and m<sub>o</sub> are the effective mass and the bare mass of the carrier, respectively. This can be used to define an approximate upper limit on the dopant concentration in the collector contact region. It is

$n \lesssim (\pi \epsilon m^* m_o E_g^2)/e^2 h^2$ .

A lower doping limit for the collector contact can also be defined. Associated with the operation of a hot electron HBT according to the invention is an emitter/collector transit time  $\tau_{ec}$ , the average time an electron spends in transit between injection into the base and arrival at the collector contact layer. This time typically is very short, of order 0.1 ps (e.g., assuming a base layer thickness Z<sub>b</sub> of 30 nm and a collector depletion laver thickness of 70 nm, with an electron velocity of 108 cm/sec). Associated with the collector contact region is a response time to the arrival of a hot electron that is the inverse of the plasma frequency. For efficient high frequency operation of the device it is desirable that this response time is much less (typically by at least about an order of magnitude) than  $\tau_{ec}$ ). This condition, combined with the previously stated condition, defines a relatively narrow doping range for the collector contact layer, and especially preferred inventive devices meet these doping criteria, which can be written as

$$(h/E_z)\lesssim (ne^2/\pi\epsilon m^*m_o)^{-\frac{1}{2}} << \tau_{ec}$$

above thickness this criterion teaches that the collector contact layer doping should be in the approximate range  $10^{19}-2\times10^{20}$  cm<sup>-3</sup>. Similar ranges are applicable for other potential collector materials.

We have also discovered that, at least under some operating conditions, a significantly improved  $f_T$  can be achieved in HBTs which incorporate into the emitter one or more appropriately placed substantially undoped

thin heteroepitaxial semiconductor layers (i.e., layers of a semiconductor other than the material of the bulk of the emitter), provided the material of the thin layers has the appropriate band structure.

The emitter charging time  $(\tau_e)$  of a HBT defines the 5 highest frequency at which the device can be operated, and is given by  $\tau_e = R_e C_e$ , where  $R_e$  and  $C_e$  are the emitter resistance and capacitance, respectively. As is well known, in conventional HBTs an increase in the doping level of the emitter decreases  $R_e$  but increases  $C_e$  and 10 thus is not very effective in reducing  $\tau_e$ .

We have found that incorporation of a relatively thin (exemplarily 1-10 nm, sufficient to prevent tunneling of holes from the base into the emitter under normal operating conditions) layer of semiconductor material of larger bandgap than the bulk of the emitter (with the offset being primarily in the valence band, with at most a small positive, preferably zero or negative, offset in the conduction band) into the emitter in close proximity to the base layer (e.g., 0-10 nm from the emitter/base interface) can result in improved majority carrier confinement in the base under high forward emitter junction bias.

We have also found that, to simultaneously achieve low Re and Ce, an additional thin (e.g., 1-10 nm, the thickness chosen to permit tunneling through the layer, resulting in the desired Re) epitaxial layer of semiconductor material (also having a wider bandgap than the emitter bulk material but having a band line-up such that the offset is primarily in the conduction band) can be incorporated into the emitter, with the spacing between the two heteroepitaxial layers typically being somewhat larger than the layer thicknesses, e.g., 10-50 nm. The spacing typically is chosen to result in the 35 desired relatively low value of C<sub>e</sub>. The bulk material between the heteroepitaxial layers advantageously is relatively lightly doped (e.g., about  $10^{16}$  cm<sup>-3</sup>) to avoid space charging effects. Incorporation of the latter thin layer permits control of Ce independently of Re, 40 whereby  $\tau_e$  can be significantly reduced. It is anticipated that this approach can result in very fast (cut-off frequency significantly above 100 GHz) HBTs, especially if the device is operated at high current densities (e.g., emitter current density greater than about 10<sup>4</sup> 45 A/cm<sup>2</sup>). At low current densities such devices however are likely to operate at somewhat lower speeds than optimized devices that do not have the additional layers in the emitter. Incorporation of these layers is optional and not a necessary feature of devices according to the 50

FIG. 4 schematically depicts the band diagram of an exemplary HBT comprising heteroepitaxial layers in the emitter. Exemplarily the emitter comprises InP, with epitaxial layer 43 (exemplarily 5 nm thick) consist- 55 ing of In<sub>0.52</sub>Al<sub>0.48</sub>As, and epitaxial layer 44 (exemplarily also 5 nm thick, 5 nm set back from the emitter/base interface, 25 nm spacing between 43 and 44) consisting of In<sub>0.45</sub>Al<sub>0.55</sub>As. The base and the collector contact 42 comprise heavily doped (p- and n-type, respectively) 60 In<sub>0.53</sub>Ga<sub>0.47</sub>As, with the collector depletion region consisting of the same material but being lightly doped or undoped. The emitter contact region is heavily doped. As will be recognized by those skilled in the art, layers 43 and 44 are strained to control the valence band/con- 65 duction band offset, and the use of strained layers is currently thought to be an advantageous approach to the tailoring of the band structure of the material of the

thin heteroepitaxial layers, and for tailoring of bandstructure in general.

FIG. 5 shows standard common emitter characteristics ( $I_c - V_{ce}$ ,  $I_b$  increased in 10  $\mu A$  steps) for an In<sub>0.5</sub>-3Ga<sub>0.47</sub>As/InP hot electron HBT substantially as described in Example 1 below, with an emitter size of  $30 \times 30 \ \mu m^2$ . The characteristic shows that the transistor has a  $\beta$  of about 200.

FIG. 6 shows similar characteristics for a hot electron HBT that differs from the transistor of FIG. 5 only in emitter size, with the former being  $0.3 \times 3 \mu m^2$ . The base current was increased in 1  $\mu$ A steps. The curves show that the transistor has  $\beta$  of about 100. Reduction in emitter size by a factor of  $10^3$  thus resulted in a decrease in  $\beta$  by only about a factor of 2, exemplifying lateral scaling, i.e., the relatively weak dependence of  $\beta$  on collector width in HBTs according to the invention.

FIG. 7 shows exemplary data on  $f_T$  vs.  $V_{ce}$  for an In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP HBT substantially as described in Example 1. Curve 70 was obtained for  $V_{be}$ =0.8 V, and curve 71 for  $V_{be}$ =0.9 V. As can be seen, the device has large  $f_T$  (exemplarily>100 GHz) over a substantial range of  $V_{bc}$ , exemplarily between 0.1 and 0.7 volt. This characteristic of inventive HBTs is of considerable technological significance, as will be recognized by those skilled in the art.

#### **EXAMPLE**

On a (100)-oriented semi-insulating InP wafer (80 of FIG. 8) was grown by gas source MBE the following sequence of epitaxial layers: a 250 nm InGaAs collector contact layer (n+,  $3\times19^{19}$  cm<sup>-3</sup>; 81 of FIG. 8); four etch stop layers (50 nm InP, 50 nm InGaAs, 300 nm InP, 50 nm InGaAs, respectively; all four layers  $n^+$ ,  $3 \times 10^{19}$ cm<sup>-3</sup>; 82, 83, 84, 85 of FIG. 8); 300 nm InGaAs collector depletion layer (n-, about  $2.5 \times 10^{16}$  cm<sup>-3</sup>; 86 of FIG. 8); 65 nm InGaAs base layer (about 50 nm being p+,  $5\times10^{19}$  cm<sup>-3</sup>, the remaining 15 nm grown with the dopant source closed; the base layer is 87 of FIG. 8); 300 nm InP emitter layer (n,  $5 \times 10^{17}$ ; 88 of FIG. 8); and a 200 nm InGaAs emitter contact layer (n+,  $7 \times 10^{19}$ cm<sup>-3</sup>; 89 of FIG. 8). All layers referred to as InGaAs have composition In<sub>0.53</sub>Ga<sub>0.47</sub>As. The n-type dopant was Si, the base was doped with Be, and the emitter contact layer with Sn.

Onto the emitter contact layer was deposited a silicon nitride layer which was patterned by conventional means so as to define the emitter stripe geometry. The nitride stripe had dimensions  $4\times4~\mu\text{m}^2$ . The wafer was then etched in 1H<sub>2</sub>SO<sub>4</sub>:1H<sub>2</sub>O<sub>2</sub>:10H<sub>2</sub>O at 0° C. until the emitter contact layer was removed except where it was protected by nitride, the remaining contact layer material being slightly etched back, forming an undercut. This was followed by an etch in 0° C. 3HCl:1H<sub>2</sub>O which etched the InP emitter layer until it was also slightly undercut. Next the nitride was plasma removed and a photoresist layer applied and patterned to define the base mesa. The base mesa was etched in the 1:1:10 etch as described above, followed by an etch in the 3:1 etch that patterned the InP layer 86. This was followed by sequential etching of the etch stop layers substantially as described above. Next the patterned photoresist was removed and the collector contact layer patterned by standard lithography and etching in the 1:1:10 etch. The patterned resist was then removed. The above sequence of steps was carried out such that the resulting mesa had a geometry substantially as depicted schemati-

12

cally in FIG. 8, with some overlying layers overhanging an underlying layer.

A photoresist layer was then applied and patterned to define the emitter, base, and connector contacts, and 20 nm of Ti followed by 70 nm of Au evaporated onto the 5 patterned resist layer. Lift-off of the unwanted metal left the self-aligned metal contacts (901, 902, 903 of FIG. 8) in place, with the contacts being spaced apart from the overlying layers, substantially as shown in FIG. 8. Next a 280 nm SiO<sub>2</sub> layer was deposited by a 10 conventional (low temperature) technique, followed by patterning of the layer to open up windows to the underlying contacts. Finally, metal was deposited and patterned in a standard final metal lithography step. The last two layers are not shown in FIG. 8.

Among the thus produced HBTs was one approximately having a  $0.3\times3~\mu\text{m}^2$  emitter stripe, a  $6\times11~\mu\text{m}^2$ collector depletion region, and a 15×20 µm<sup>2</sup> collector contact region. For Veb=0.9 V the transistor had  $E_i \sim 200$  meV. With  $V_{eb} = 0.9$  V and  $V_{bc} = 0.4$  V the 20 47As. transistor had fr of 110 GHz and a DC current gain of 50.

The above described exemplary procedure results in a device that comprises regions (e.g., the emitter stripe and the collector depletion region) that are undercut in 25 controlled fashion. We consider such undercutting to be a significant aspect of the invention since it permits self-aligned contact formation and generally is a contributing factor in the attainment of high speed, due to the resulting reduction in, e.g., collector capacitance.

We claim:

- 1. A heterostructure bipolar transistor comprising a collector region, a base region, and an emitter region, and further comprising means for making electrical contact with the emitter, base, and collector regions, 35 comprising semiconductor material having an intrinsic respectively; the transistor being of the type wherein, under normal emitter/base forward bias conditions, hot electrons are injected into the base region from the emitter region; associated with the transistor being structural features including a width W of the emitter 40 region, a base region thickness, a base region dopant concentration, and a base region surface that comprises, in addition to a portion that is overlain by the emitter region (this portion to be referred to as the "intrinsic" base region surface), a further portion that is adjacent to 45 means for making electrical contact with the base rethe emitter region and is not overlain by the emitter region, the further portion to be referred to as the "extrinsic" base region surface; wherein

- a) the emitter and collector regions comprise n-type III-V semiconductor material and the base region 50 comprises p-type III-V semiconductor material;

- b) the width W is at most 1 µm, the base region thickness is less than 100 nm, and at least a portion of the base region has a dopant concentration of at least  $2 \times 10^{19} / \text{cm}^3$ ;

characterized in that

c) the emitter region comprises at least a first and a second semiconductor material, associated with each of the first and second materials being a valence band edge and a conduction band edge, the second material having a bandgap that is wider than the bandgap of the first material, with the offset between the first and second material valence band edge being greater than half the difference between said bandgaps, a layer of the second material being epitaxial with the first material and being situated relatively close to the emitter region/base region interface and being substantially undoped, with the second material layer thickness selected to substantially prevent tunneling of holes from the base region into the emitter under normal emitter/base forward bias conditions.

- 2. A transistor according to claim 1, wherein the 15 offset between the first and second material conduction band edge is zero or negative, and wherein said second material layer is a strained layer.

- 3. The transistor of claim 1, wherein said semiconductor material has approximate composition In<sub>0.53</sub>Ga<sub>0.</sub>

- 4. The transistor of claim 1, wherein the second material layer has a thickness in the range 1-10 nm.

- 5. The transistor of claim 4, wherein the emitter region comprises a further relatively thin, undoped or unintentionally doped, layer of a third semiconductor material epitaxial with the first material, the third material also having a bandgap that is wider than the bandgap of the first material, the spacing between the two relatively thin layers being larger than the thickness of 30 either of the layers, with one of the two layers being spaced a distance in the range 0-10 nm from the interface, the material between the two layers being lightly doped first material.

- 6. A transistor according to claim 1, the base region surface recombination velocity  $S_o$ , wherein the means for making electrical contact with the base region comprise a non-alloyed metal contact, a degenerate semiconductor contact or a combination of a non-alloyed metal contact and a degenerate semiconductor contact, the contacts formed such that the surface recombination velocity on the extrinsic base region surface is not substantially greater than  $S_o$ .

- 7. A transistor according to claim 1, wherein the gion comprise a non-alloyed metal contact, a degenerate semiconductor contact, or a combination of a nonalloyed metal contact and a degenerate semiconductor contact, wherein at least a portion of the collector region contains a dopant concentration greater than about  $10^{19} \text{ cm}^{-3}$ .

- 8. In combination, a transistor according to claim 1, wherein the transistor is situated on a semiconductor substrate, with at least one other electronic or opto-55 electronic device also situated on or in the substrate, and with conductive means providing a conductive path between the transistor and the at least one other device.